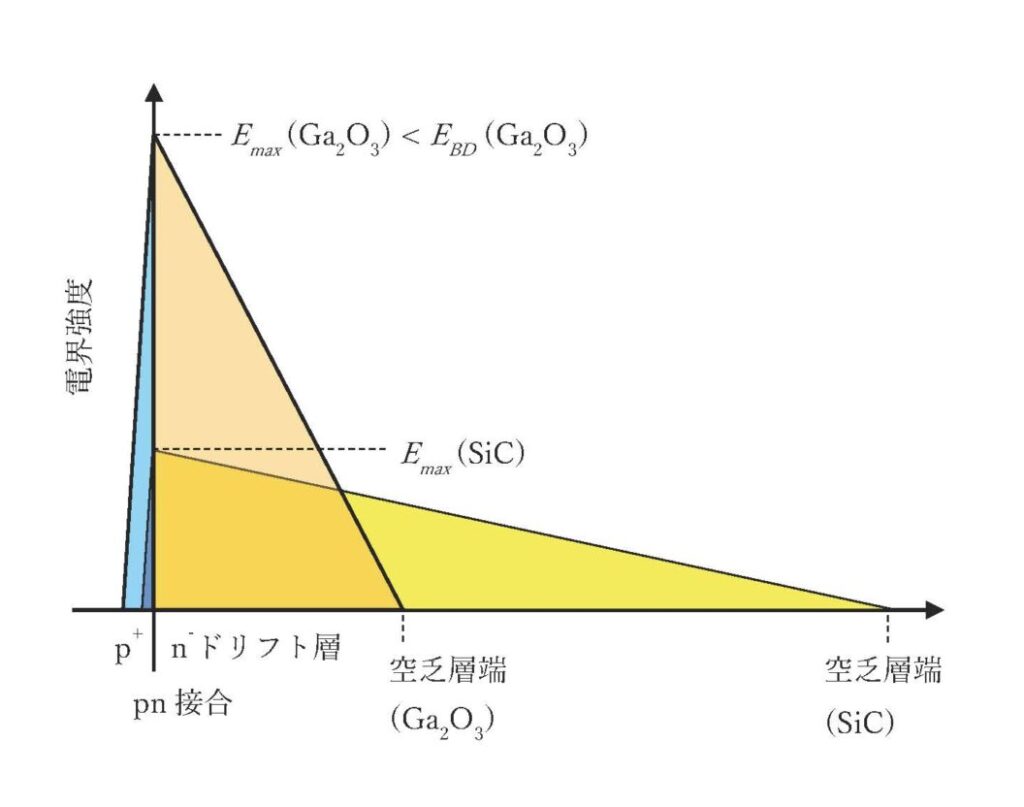

パワー半導体デバイスの解説では、pn接合のn–ドリフト層側に広がる空乏層の電界分布の図を使って、最大電界と空乏層濃度と耐圧の関係を説明する。空乏層がn–ドリフト層内に止まることを前提としたノンパンチスルー(NPT)型である。ところが実際のパワー半導体デバイスでは、空乏層が必ずしもn–ドリフト層内にで止まらないパンチスルー(PT)型の設計が多用されている。本記事では、同じ耐圧を持つNPT型とPT型のドリフト層抵抗を比較して、パワーMOSFETのドリフト層設計の最適化を考える。

〜 イノベイティブな半導体、エレクトロニクス、エネルギー技術のソルーション 〜

Innovative Semiconductors, Electronics, & Energy Solutions

カテゴリー一覧

アーカイブ

- 2025年4月

- 2025年3月

- 2025年2月

- 2024年11月

- 2024年10月

- 2024年8月

- 2024年7月

- 2024年6月

- 2024年5月

- 2024年4月

- 2024年3月

- 2024年2月

- 2024年1月

- 2023年12月

- 2023年11月

- 2023年10月

- 2023年9月

- 2023年8月

- 2023年7月

- 2023年6月

- 2023年5月

- 2023年4月

- 2023年3月

- 2023年2月

- 2023年1月

- 2022年12月

- 2022年6月

- 2022年4月

- 2022年3月

- 2022年2月

- 2022年1月

- 2021年12月

- 2021年11月

- 2021年10月

- 2021年9月

- 2021年8月

- 2021年6月

- 2021年5月