5/30~6/3にリモート開催されたISPSD2021では、SiCのFinFETがひとつのトピックだった。今日のコラムでは、SiCパワーデバイスにおけるFinFETの意味を考えてみよう。

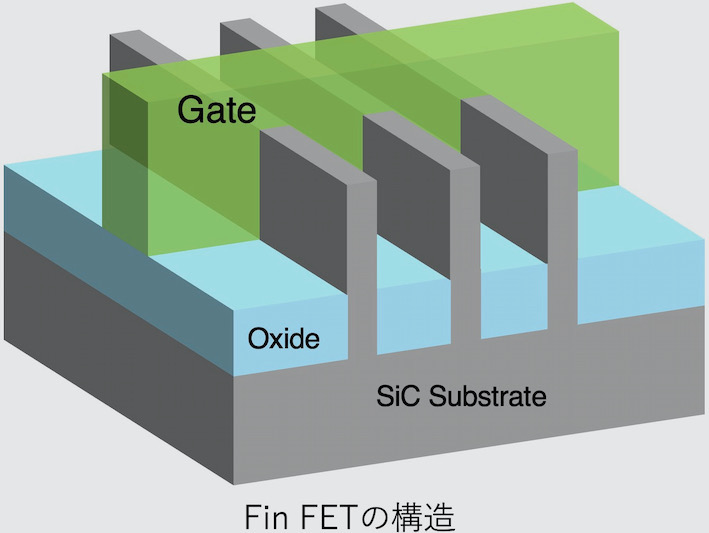

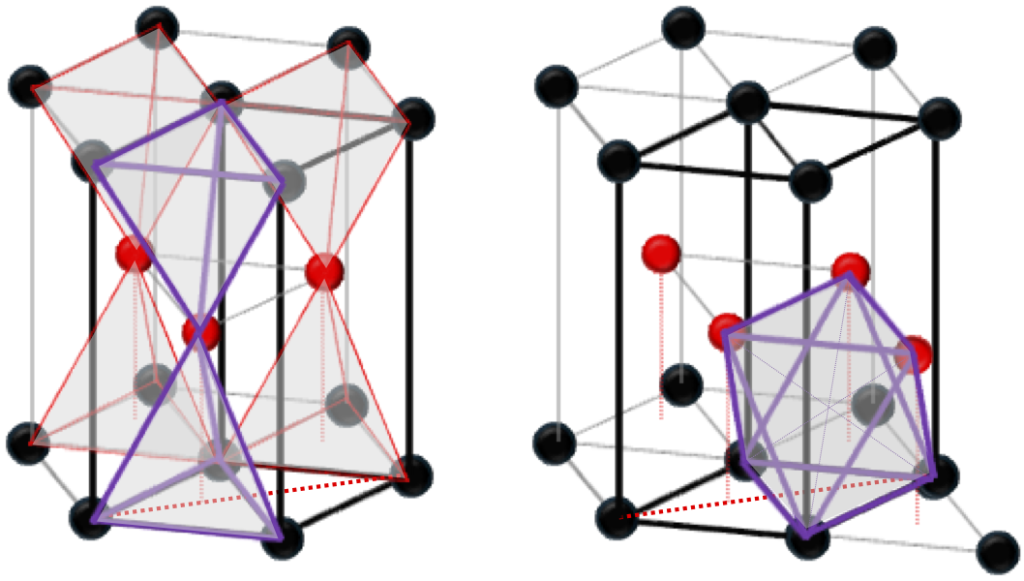

FinFETはSi MOSFETの微細化を進めるために開発された構造で、いわゆる20nm世代以降のLSIで用いられている。ウェファの表面に異方性エッチングで屏風状のSiチャネルを形成し、両側から挟んだゲートでチャネルの電位を支配して、短チャネル効果を抑え込む。また、Finを高くしてピッチを詰められれば、同じフットプリントのプレーナトランジスタよりもゲート幅を大きくでき、電流駆動力が向上する。

SiCパワーデバイスでFinFETを採用する意義を考える。短チャネル効果を抑えてゲート長を短縮できれば、ON抵抗のチャネル抵抗成分が小さくなる。同じフットプリントでゲート幅を長くできれば、同一チップサイズでチャネル抵抗が下げられる。日立のTED-MOSはこの発想と聞いている。

ISPSDでは、上の効果とは別に、FinFET構造にするとチャネルの移動度が大きく上がることが注目された。移動度が改善すればON抵抗のチャネル抵抗成分が改善される。それが桁のオーダーだというので話題となったのである。

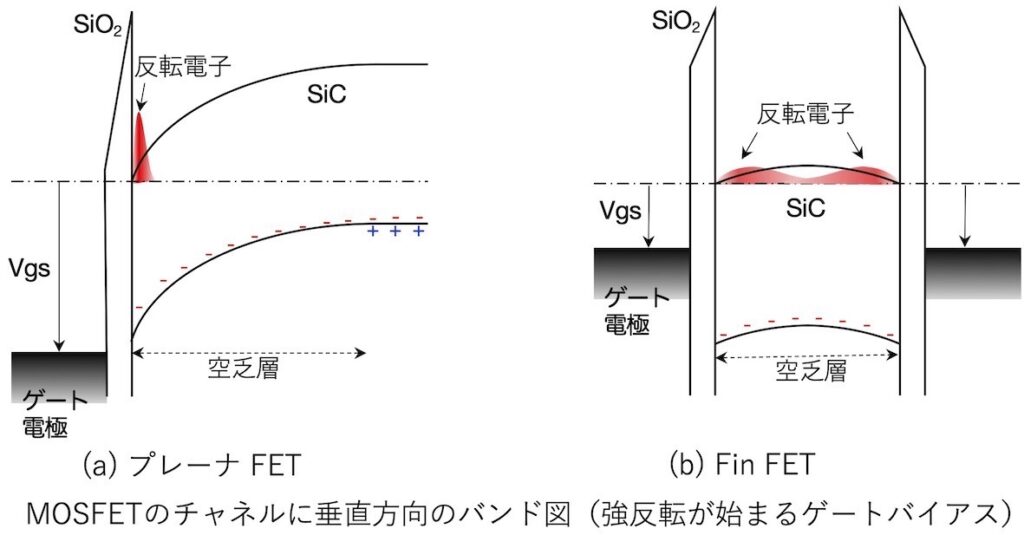

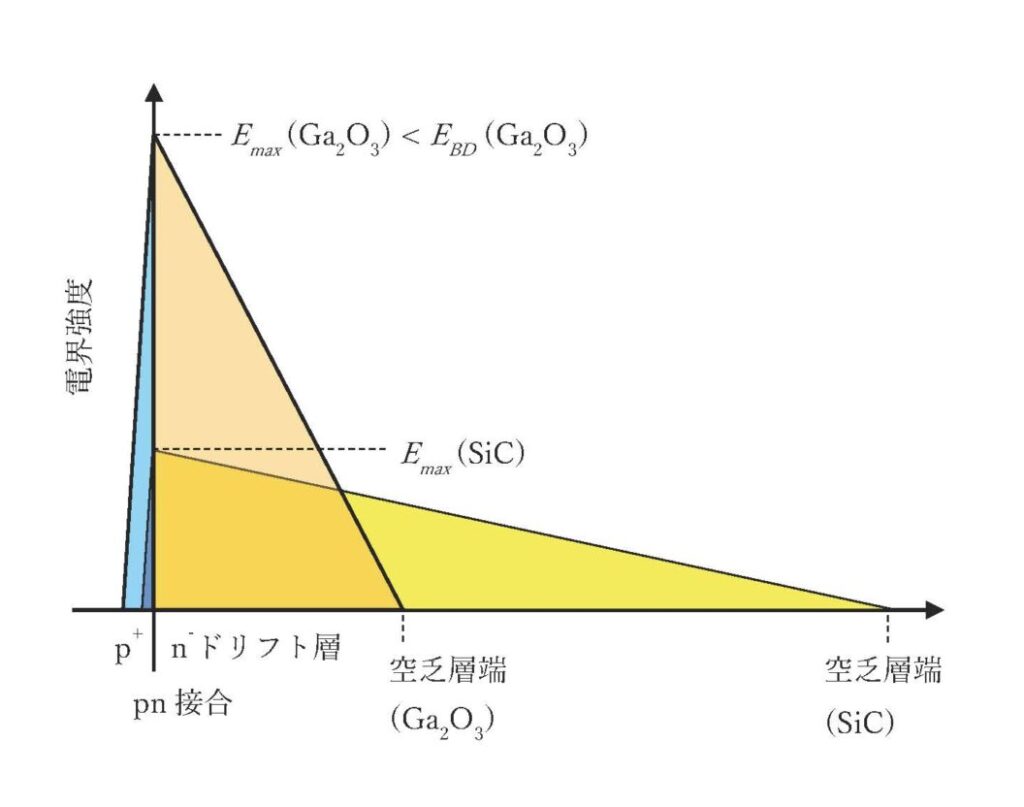

このメカニズムを簡単に解説する。MOS界面のキャリア移動度は、MOS界面の実効電界Eeffに依存する。Eeffが大きくなるほど反転層のキャリアがMOS界面に押し付けられる。MOS界面にはキャリア散乱源が多数存在するので散乱確率が上がりキャリア移動度が低下する。

プレーナーMOS構造であれば、反転層が形成されているときに、ゲート電極の正電荷から出る電気力線は、反転層電子とp-body空乏層のイオン化アクセプターに終端する。つまりMOS界面には反転層を誘起する電界と空乏層を維持する電界が重畳する。

FinFETでチャネルがドーピングされていない理想的な場合を考えると、ゲートから出る電気力線は反転層電子で終端するのみ。空乏層を維持する電界が無い分、Eeffが小さくなる。

Finチャネルがドーピングされている場合は、Finチャネルのp濃度はプレーナーMOSFETのp-body濃度を上限とすると考えてよいだろう。この場合、Fin厚み(の半分)は、プレーナーの最大空乏層厚よりも薄く設計されるはずである。FinFETを採用して移動度を上げる効果を出すためには、チャネルを完全空乏化して反転層をMOS界面から離さないと意味が無いからである。

p濃度が同じプレーナMOSFETとFinFETのバンド図を半定量的に描いてみた。Finの厚みはプレーナーの最大空乏層厚の80%とした。FinFETでは、Eeffが小さくなり反転電子の分布がMOS界面から離れることがわかる。

別の言い方をすれば、FinFETではFinを薄くして、完全空乏したFinの面電荷密度をプレーナーMOSFETよりも減らすことで、Eeffを小さくして、チャネル移動度を高めるのである。

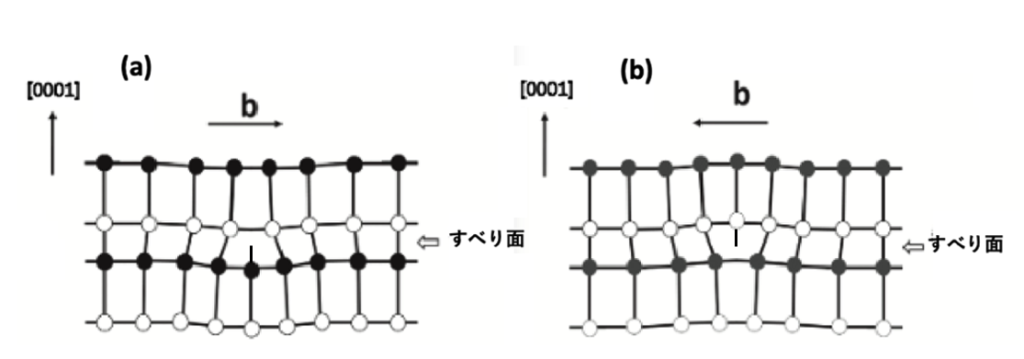

気になるのは、FinFETで反転層ができる前のチャネル電位はどう決まるのかという疑問。プレーナーならば、MOSキャパシタを考えて、p-bodyの空乏層が伸びることで表面電位が動くと理解できる。FinFETの断面図を見ても、反転層形成前には、ゲートから出る電気力線の行き先の負電荷がどこにもない! FinFETって本当に反転層が形成できるの???

これは、FinFETの3次元構造を考えて、断面図に無いソース電極を考えればよい。FinFETではp-bodyに相当する電極がないので、キャパシタとしてもゲート電圧はゲートとソース間にかかる。つまり、ゲートから出る電気力線はソースに終端する。そうして、ソースに近いFinチャネルの表面電位がフェルミレベルより下がったときに反転層ができ始める。

これからわかるように、FinFETの閾値は、nポリSiゲート / 酸化膜 / 低濃度のp–SiC / n+SiCソース のバンドラインアップで決まる。上の議論から、FinFETにして移動度を上げるというメリットを出すためには、チャネルをpドープしたとしても、プレーナーMOSFETと比べて、閾値が小さくなることが避けられない。これは上のバンド図のVgsの違いに現れている。

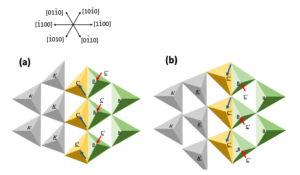

Si-FinFETでは、ゲート材料をnポリからメタルに替えて仕事関数を大きくすることで、閾値を維持している。メタルゲートが高温プロセスに耐えられないため、ポリSiゲートを形成してからソースドレイン注入とアニールを行う従来のゲートファーストプロセスから、ソースドレイン注入アニール後にゲートスタックを形成するゲートラストプロセスに変更を余儀なくされた。SiC MOSFETはもともとゲートラストプロセスだが、その後に高温のコンタクトアニールが控えている。

FinFET構造をパワーMOSFETに適用するには、Fin加工の難しさがまず目に付くが、適正な閾値の実現がそれ以上に難しい課題である。

(坂本邦博)

コメントを残す