(F) n–ドリフト層の側面からの格子欠陥の侵入

・(F-1)トレンチMOS縦型界面の場合

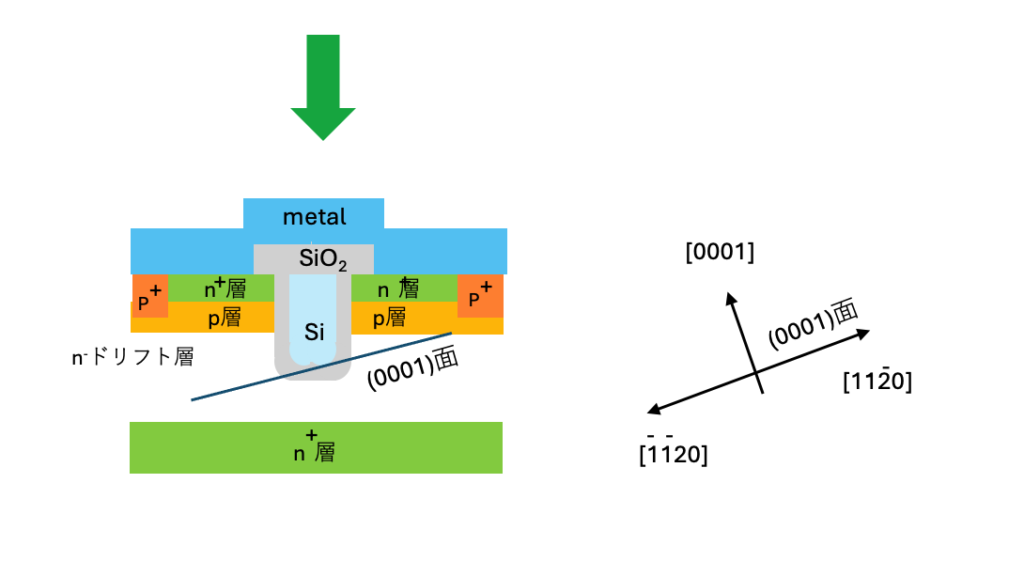

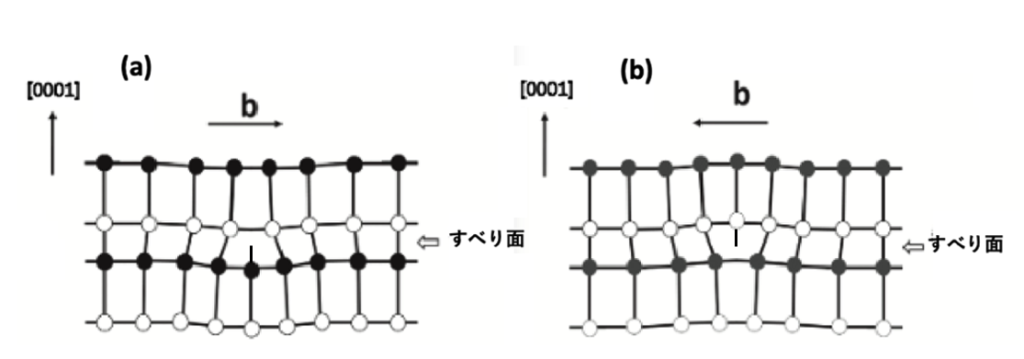

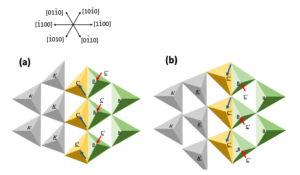

(F)はn–ドリフト層の側面から基底面転位などの格子欠陥がn–ドリフト層へ侵入してくる状態を想定しています。(F-1)はトレンチMOSの縦型MOS界面から基底面転位などのn–ドリフト層への侵入を想定して考察しています。図12-5(a),(b),(c),(d),(e)は縦型MOS構造の[1120]側での縦型MOS界面とp層の間のn–ドリフト層で成長する積層欠陥の形状をMOSFET構造の上側から観察した状態を示します。図12-5 (a’),(b’),(c’),(d’),(e’)は縦型MOS構造の[1120]側での縦型MOS界面とn+層の間のn–ドリフト層で成長する積層欠陥の形状を示します。黒丸は発生源となった基底面転位の位置を示しています。想定しているトレンチMOS構造と、観察方向と、積層欠陥の載っている基底面の幾何学関係は図11-6に示します。図12-5の積層欠陥の形状は図12-1を参考にして描いています。

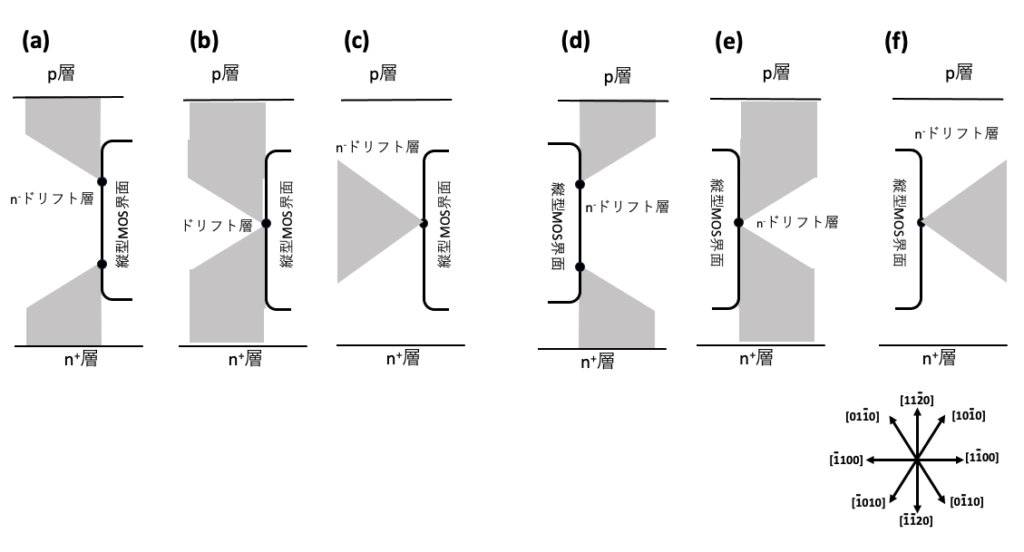

図12-6 (a),(b),(c)は縦型MOS構造の[1100]側での縦型MOS界面からn–ドリフト層へ成長する積層欠陥の形状を示しています。(d),(e),(f)は縦型MOS構造の[1100]側での縦型MOS界面からn–ドリフト層へ成長する積層欠陥の形状を示しています。黒丸は積層欠陥の成長源となった基底面転位の位置を示しています。図12-6 (a)は単体の菱形積層欠陥が成長する例です。この場合最終的に三角形の形状かあるいは四角形の形状で成長は飽和します。図12-6 (b)は2重菱形積層欠陥成長の場合を示しています。図12-6 (c)は六角形状積層欠陥が成長する場合の図です。これらの図は図12-3を参考に描いています。

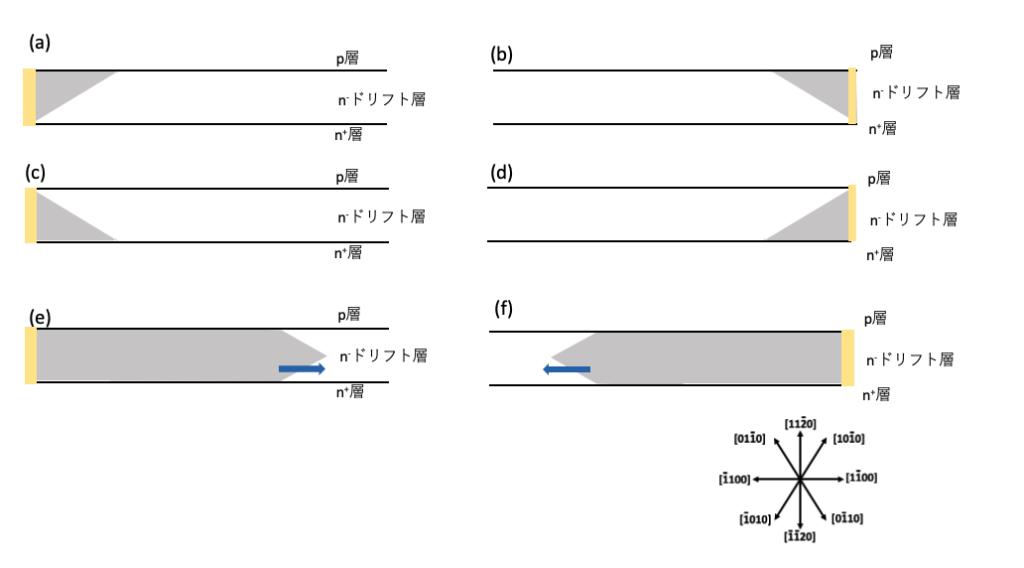

図12-7 はダイシングにより、MOSFETの側面処理部分を突き抜けてSiコア部分転位と積層欠陥がn–ドリフト層部分に侵入した場合に形成される積層欠陥の形状を示しています。MOSFETの側面は、側面での電流リークを防ぐために周辺耐圧構造層を形成していて、この側面耐圧構造層は10ミクロン単位程度の厚さで設計されています。ダイシング時にこの層を突き抜けてSiコア部分転位と積層欠陥がn–ドリフト層に侵入して来ることは起こりづらいと考えられますが、ここでは、側面からSiコア部分転位がn-ドリフト層部分に侵入した場合を一応想定して考察しています。図17(a),(c),(e)はMOSFETの [1100]側端面から積層欠陥が成長している場合です。図17(b),(d),(f)はMOSFETの [1100]側端面から積層欠陥が成長している例です。

図17(a),(b),(c),(d)で示しているような直角三角形状の積層欠陥が形成され積層欠陥の成長が停止する場合と、図17(e),(f)で示しているような先端が三角形状の積層欠陥が片方の端から、もう片側の端に向かって成長する場合があることがわかります。青い矢印は積層欠陥の成長の方向を示しています。

n–ドリフト層の下側から入ってくる基底面転位、上側から入ってくる基底面転位、側面から入ってくる基底面転位、n–ドリフト層内部で発生する基底面転位、界面転位や界面転位に関連した転位組織、のそれぞれ異なる素性の基底面転位から成長する場合は、積層欠陥の形状がそれぞれ異なることがわかります。これがこの連載の重要な結論です。

図12-1から図12-7までで示された図と観察された形状より、特性劣化を引き起こす積層欠陥の原因となる基底面転位の素性が明らかになるかもしれません。デバイスプロセスの改善や、ウエハそのものの改善点がわかるかもしれません。MOSFETに順方向特性劣化が発生した場合実際に顕微PL法や、放射光X線トポグラフ法で積層欠陥を観察すると、多数の積層欠陥が重なったものが観察されて解析が困難になっている場合もあります。積層欠陥の成長初期に観察すると、重なり部分が少なく解析しやすいと思います。

10年以上前のNEDOプロジェクトで筆者が観察していた時は、 (A),(B),(C)が原因の積層欠陥の成長が圧倒的に多数でした。それらは報告書や論文として発表されています。現在では、発生原因(A),(B),(C)の抑制はある程度進んでいると推察されます。 特に(A)の抑制は、n–ドリフト層のエピ成長の前に、n+バッファー層や再結合促進層などを挟むことなどの特許技術は効果的だと議論されています。これについては、T. Kimoto & H. Watanabe, Appl. Phys. Express 13 120101 (2020)に説明があります。 (A),(B),(C)が抑制されると、他の原因によるものもそれなりに見つけられるのではと推察します。ここで紹介した (D),(E),(F)による積層欠陥の形状は推察によるものです。(D),(E),(F)の場合は、こんなモデルで考察するとこういう形状の積層欠陥の成長が推察されます、という話を示しました。

この解説はSiC-MOSFETの特性劣化現象が発生した際に現れる積層欠陥の形状について整理しました。そしてその形状から基底面転位の素性が推察されます、という話を解説しました。SiC-MOSFETの特性劣化の対策の参考になればと思います。ご精読ありがとうございます。

この連載の解説文の一部については、筑波大学 関口隆史教授から助言をいただきました。また、ISEES-LLPのメンバーからも色々と助言を受けました。感謝いたします。

この解説文は以下の文献を参考にしました。

X. J. Ning & P. Pirouz, J. Material Research 11 884-894 (1996).

S. J. Maximenko et al., Appl. Phys. Lett. 87 033503 (2005).

M. Skowronski & S. Ha, J. Appl. Phys. 99 011101 (2006).

N. Zhang, et al., Appl. Phys. Lett., 94 122108 (2009).

B. Chen et al., J. Appl. Phys., 106 074502 (2009).

B. Chen et al., Phy. Rev. B 81 233203 (2010).

X. Zhang et al., Mat. Sci Forum Vol. 679-680 pp306 (2011).

H. Matsuhata et. al., Philos. Mag. 94 1674 (2014).

松畑ら、電気学会論文誌A 135 pp768 (2015).

A. Tanaka et al., J. Appl. Phys. 119 095711 (2016).

A. Iijima et al., Philos. Mag. 97 2736 (2017).

H. Matsuhata & T. Sekiguchi, Philos. Mag. 98 878 (2018).

T. Kimoto & H. Watanabe, Appl. Phys. Express 13 120101 (2020).

松畑 & 関口、日本結晶学会誌62 150 (2020).

J. Nishio et al., Jpn. J. Appl. Phys. 61 SC1005 (2022).

(完)

コメントを残す