日本の半導体復活を目指す動きが湧き上がり、業界が色々とかまびすしい。経産省の肝入りで昨年設立されたRapidusは、「2nmノードのLSI」の製造を目指すと言っている。2nmノードのトランジスタとはどのようなものになるのだろうか。IBMのナノシート技術(積層型 Gate All Around: GAA 構造)を導入することが明らかにされているが・・・

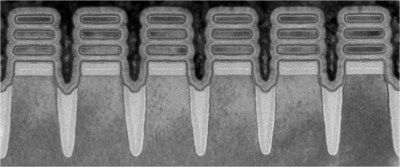

IBMプレスリリースのAdditional Assets, Row of 2 nm nanosheet devicesより

最先端ロジックを開発するメーカーが少数になるにつれ、学会で発表される技術情報が少なくなり、トランジスタのスペックやプロセスが見えにくくなっている。

そんな折に、1/27に開催されたAIチップ設計拠点フォーラムで、東大の平本先生の先端ロジックデバイスの技術動向解説*1を聴講した。過去から現在までの流れが明快に解説されて、私なりに将来の動向を捉えることができた。それをもとに、2nmノードと更に先の技術ノードのLSIの姿を考えてみる。

ここ40年の技術動向を要約すると、

(1) 技術ノード名 (“数字”&”nm”) は、1980年代から、一貫して、ほぼ2年で1世代 (前世代の”数字” X 0.7) 進んでいる。

(2) トランジスタの実ゲート長 Lg は、2000年代前半まではノードの数字より短かったが、その後縮小が鈍化し、2010年代でノードの数字と逆転、最近は10数nmで止まっている。2022年にTSMCが発表した最新の3nmノードでは Lg = 12nmだった。報道などで、3nmというとてつもなく小さなトランジスタ、と言われるが、実のところ3nmノードのLSIで、平面寸法が3nmの構造はどこにもない。

(3) 一方で、SRAMのセル面積は引き続き縮小している。ただし2010年代から、1世代技術ノードが進むとセル面積が半分になるトレンドラインから遅れてきている。

個々のトランジスタの性能に注目すると、

(4) トランジスタ単体のスイッチング時間の性能指標 CV/I は、技術ノードが進むににつれて短かくなり、2000年ごろ1psに達したが、その後は足踏み。

(5) トランジスタ単体のスイッチングエネルギーの性能指標 CV2/2 は、ドレイン電圧 V の低下が止まった2010年ごろからほぼ一定。

(6) 実効ゲート酸化膜厚 Tinv は、2000年代半ばから1nm程度で下げ止まっている。

トランジスタ技術では、ここ20年に、2007年のゲート高誘電率酸化膜・金属ゲート (HKMG) の導入と2012年のFinFET構造の導入という二大革新があった。

これらのトレンドをざっくり整理すると、HKMGとFInFETの導入以降、Dennardの定電界スケーリングが打ち止めとなり、トランジスタ固有の性能向上は20-14nmノードで止まっていることがわかる。

それにもかかわらず、14nm以降のノードでも引き続き、SRAMのセル面積が縮小し、LSIの性能(消費電力あたりの処理能力)の向上が続いている。その理由を考えよう。スイッチング時間とスイッチングエネルギーの性能指標に出てくる容量 C に注目する。Cには配線容量が含まれていない*2。先端LSIのトランジスタが駆動しなければならない最も重い負荷はこの配線容量だ。トランジスタ単体の性能が向上しなくても配線容量を減らすことができれば、スッチング時間や消費電力で測られるLSIの性能が向上する。

配線容量の削減は二つの方法で実現されてきた。ひとつは、トランジスタが小さくできなくとも、それ以外の素子分離やコンタクトのスペースを切り詰めて、SRAMのセル面積や論理ゲートの占有面積を縮小する方法だ。そのためにリソグラフィー精度に頼らない自己整合プロセスが駆使されている。SRAMのセルや論理ゲートの占有面積が小さくなれば、その内部接続配線と内外を結ぶ配線がともに短くなり、配線容量が削減される。

もうひとつは、FinFETのFinの高さを高くしたのだ。Finを高くすれば、トランジスタの平面寸法を増やさずに、実効ゲート幅 W を伸ばしてFin1本に流せる電流を増やすことができる。その結果、論理ゲートを構成するトランジスタのFinの本数を減らすことができ、論理ゲートの占有面積を小さくして、配線容量を小さくできる。

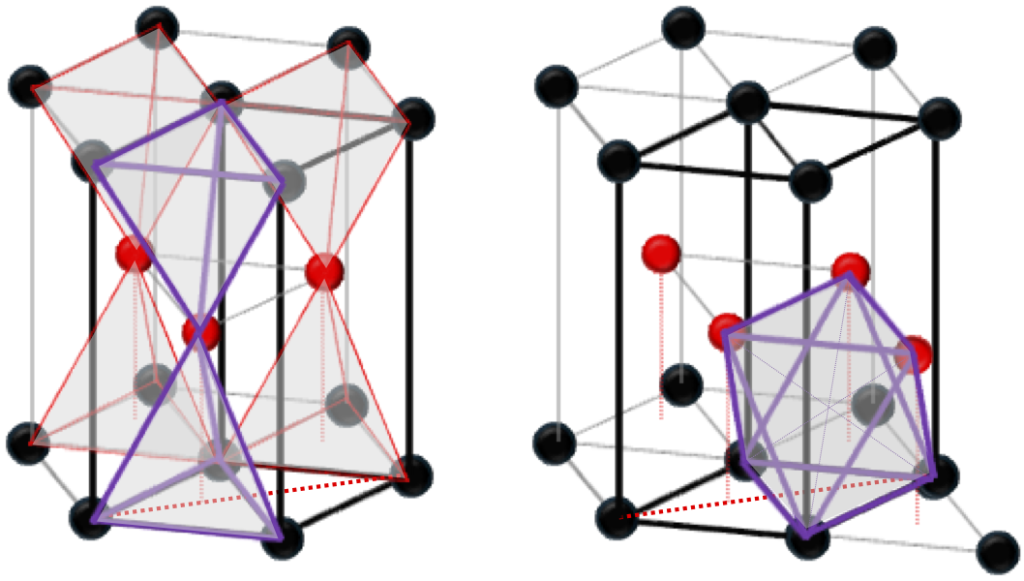

この視点から、2nmノードのナノシートトランジスタを見直してみよう。従来のFinFETからの大きな変化は、薄い半導体ナノシート層を積層したGAA構造になることである。製造プロセスは大きく変更され、原子層単位で制御する Atomic Layer Deposition, Atomic Layer Etchingのような精緻なプロセスが求められる。電気特性から見ると、HKMGが変わらないので、トランジスタ固有の性能指標 CV/I, CV2/2 の大きな向上は無いだろう*3。そうすると2nmノードトランジスタに期待されるのは、チャネルを縦積みにすることでトランジスタ占有面積あたりの W を増やすことであり、上記第2の方法で配線長を短縮することが主眼であることが見えてくる。

このように、トランジスタ固有の性能指標が向上しない時代の技術ノードの肝は、なんとかして演算機能をコンパクトに縮小して配線を短くすることにある。先の技術ノードを目指し、トランジスタの革新と並行して、電力供給配線をトランジスタの裏側に形成するPower Rail構造の開発が進められている。チップ上面は信号配線だけにして配線やコンタクトに割くスペースを大きく減らし、論理ゲートの占有面積をさらに小さくする狙いだ。

その先には、トランジスタ自体を何層も積層する 3D LSIの構想がある。二次元平面に並ぶトランジスタ間で取り回していた配線を、上下のトランジスタを結ぶ層間配線に置き換えれば、配線はぐっと短くなる。信号が縦横上下の三次元に走り回るその姿は脳の神経回路網のようでもある。

3D LSIは、今日の半導体業界を賑わす話題のひとつだが、長い研究開発の歴史がある。40年前、微細化の限界が1μmと言われていた頃、これ以上小さくならないなら上に積めとばかりに、三次元にトランジスタを積み上げる構想があった。当時の通商産業省で「三次元回路素子」と題した研究開発プロジェクトも行われ、筆者も一部に関わっていた。当時の大きな課題として、三次元化したLSI内部の発熱をどうやって逃すのかという議論があった。

LSIではチップ裏面のSiウェハ側から熱を逃すが、積層したチップの発熱を逃す経路はSiウェハ厚み分のチップ側面しかない。大した消費電力でなくても使用上限温度を突破してしまう恐れがある。積層した各層に冷却用のマイクロ流路を作り込んで冷媒を流せば冷やせる、という論文があったのを覚えている。幸い1μmの壁はリソグラフィーの短波長化と電圧スケーリングで克服されて、マイクロ冷却管の出番はなかった。

2nmノードから先の発熱問題を考えてみよう。トランジスタ1個のスイッチングエネルギー CV2/2 をLSIチップ全体に拡張してチップ全体の消費電力を考る。トランジスタの総数を N、クロック周波数を f、トランジスタひとつの容量を CFET、それが駆動する配線容量を Cwire とすると、LSIの消費電力 P は、次の式で見積もることができる

P = f N ( CFET + Cwire ) V2 /2

1μmの時代は、トランジスタを微細化して CFET + Cwire を小さくし、同時に酸化膜厚を薄くして V を小さくできた。その結果、消費電力 P を増やすことなく、集積度 N を上げかつ処理速度 f を上げることができた。当時は困難な技術開発であったが、今では Happy Scaling Era と呼ばれる時代である。

2010年代以降にトランジスタ固有の性能指標が飽和すると、もはや V や CFET を小さくできなくなった。ここまで論じてきたように、なんとか論理ゲートの占有面積を小さくして Cwire だけでも減らして消費電力 P を抑える戦略になっている。CFET << Cwire で ある間はこの戦略が通用するが、 CFET ≒ Cwire に至ったときに、消費電力がSi LSI微細化に引導を渡すことになる*4。

(坂本邦博)

*1

講演で示された図表は、平本先生の2020年VLSI-TSAの発表の図表に最新の動向を追記したものだった。たいへんよく纏められているので、興味ある方は元の論文をご覧くだい。

*2

C はトランジスタのゲート容量とトランジスタ構造内の寄生容量の和。配線容量は含まない。V はドレイン電圧、I はドレイン電流。

*3

トランジスタ構造をFinからGAAに変えると、ゲート電極のチャネル電位支配力が増して、短チャネル効果が抑えられることが期待されるが、FinFETのゲートがチャネル長方形断面の2長辺と1短辺に作用するのに対しGAAでは短辺ひとつが加わるだけなので、ゲート支配力の大きな向上は期待できない。GAA構造にしてもゲート長は縮めず、ゲート支配力向上をリーク電流抑制に振り向けて、スタンバイ電力を抑えるのが上策だろう。

(2025年春の応用物理学会で入手した情報をもとに 2025.3.17 追記) IEDM2024で、TSMCから2nmプラットフォームの発表があった。ナノシートFETのSubthreshold Swing (SS値) は 68 mV 。前世代の3nmFinFETとSS値が変わらず、ゲート支配力が向上していないことがわかる。ならばどうして3nmから2nmノードに進むと性能が20-30%も向上するのだろうか。鍵は閾値電圧 (Vth) のばらつきにある。FinFETはリソグラフィーとエッチングでFinチャネルを形成する。ナノシートFETではSi/SiGeのエピタキシャル成長で半導体チャネルを形成する。チャネル厚さの均一性は、Finでは微細加工のウェハ面内均一性に依存し、ナノシートではエピの膜厚の面内均一性で決まる。半導体プロセスに詳しい人なら平面寸法よりも膜厚の精度が高いのが理解できるだろう。つまりFinFETからナノシートFETになると、チャネル厚さの均一性が良くなることが期待される。微細MOSFETのVthはチャネル厚さに敏感なので、ナノシートFETのVthばらつきがFin FETのVthばらつきよりも小さくなるはずだ(Vthばらつきは製造ラインの実力を反映する最高機密なので半導体製造企業が発表することは無い)。FETがオフの時のリーク電流はVthが小さくなると指数関数で増大する。一方、LSIを構成する多数のFETのVthは正規分布をとる。従って、Vth分布の小さい方の裾にいる少数のFETが、LSI全体のスタンバイ電力を決めることになる。LSIの設計はワーストケースを想定して行われるので、Vthのばらつきが小さくなれば、それ以外の特性が向上しなくてもスタンバイ電力が小さなLSIを設計することができる。また同じスタンバイ電力で良ければ、Vthを下げて動作速度を向上できる。このように、Finからナノシートへ基本構造が変わってVthばらつきが小さくなることが、3nmノードから2nmノードでLSI全体の性能が向上する最も根源的な理由と考えられる。この手は基本的に一回使うと終わりである。TSMCの次の一手は、本文で触れたPower Rail構造。2nmノード改良版で導入するとアナウンスされている。

*4

回路アーキテクチャからも消費電力を抑える取り組みが行われている。処理能力を必要としないときにクロック周波数 f を落とす Clock Gatingや、使っていない回路の電源電圧 V を落とす Power Gatingなどの様々な技術が導入されている。放熱が難しくなる3D LSIでは、高速で動作するのはごく一部で全体はゆっくり動作するようなアーキテクチャにならざるを得ないだろう。これはまさに脳の活動パターンで見られるものだ。ちなみには脳には微細な流路を持つ液冷システムが(血管)張りめぐらされている。

コメントを残す